# ENGN2219/COMP6719 Computer Systems & Organization

#### Convener: Shoaib Akram shoaib.akram@anu.edu.au

Australian National University

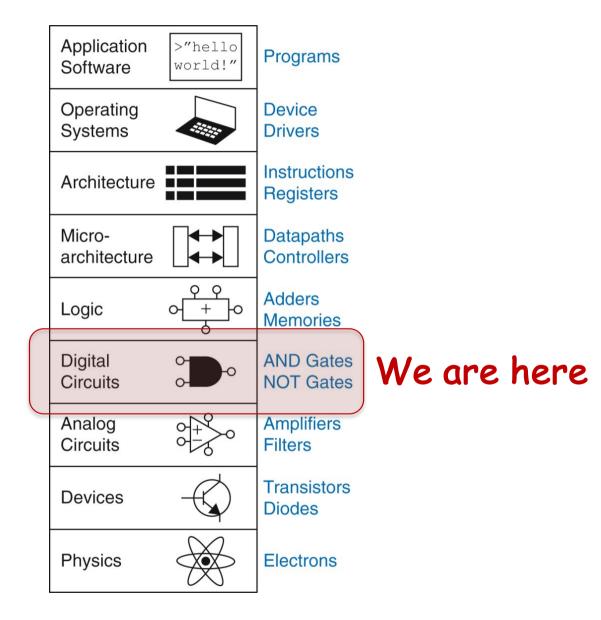

# Plan: Week 2

Week 1: Digital abstraction and binary digits

Week 2: Number systems for binary variables, Logic gates

This Week: Boolean logic & Logic gates (contd)

This Week: Combinational logic (more than just gates)

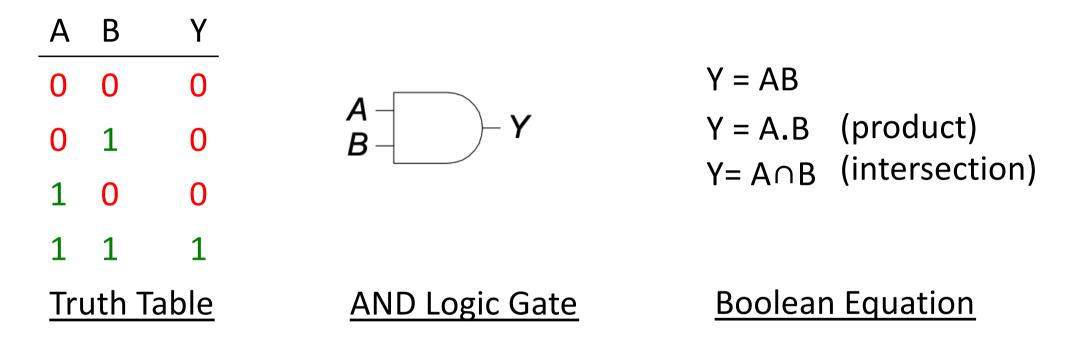

## **The AND Function**

AND Function: The output Y is 1 if and only if both A and B are 1

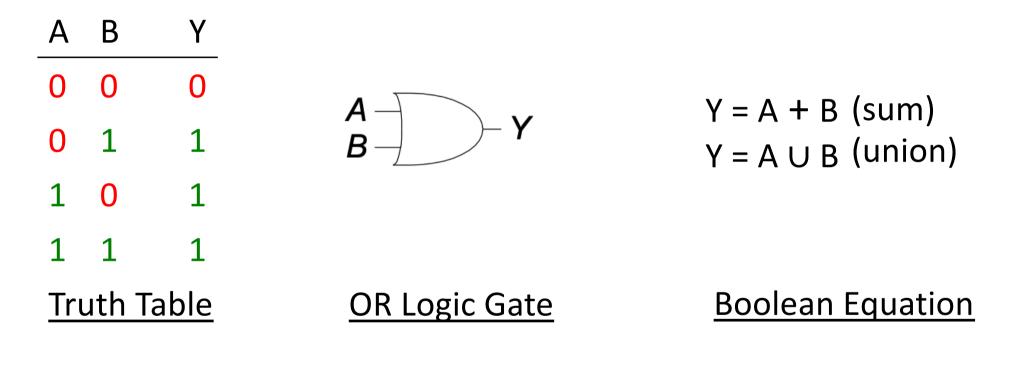

# **The OR Function**

AND Function: *The output Y is 1 if either A or B are 1*

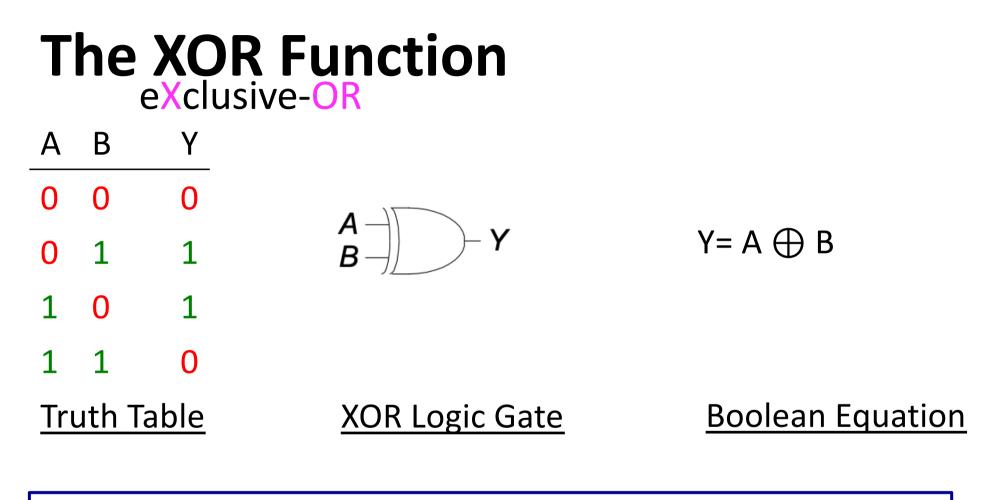

AND Function: *The output Y is 1 if A or B, but not both, are 1*

# Terminology

The term *exclusive* is used because the output is 1 if only one of the inputs is 1

The OR function, on the other hand, produces an output 1, if only one of the two sources is a 1, or both sources are 1 (think of it as *inclusive* OR)

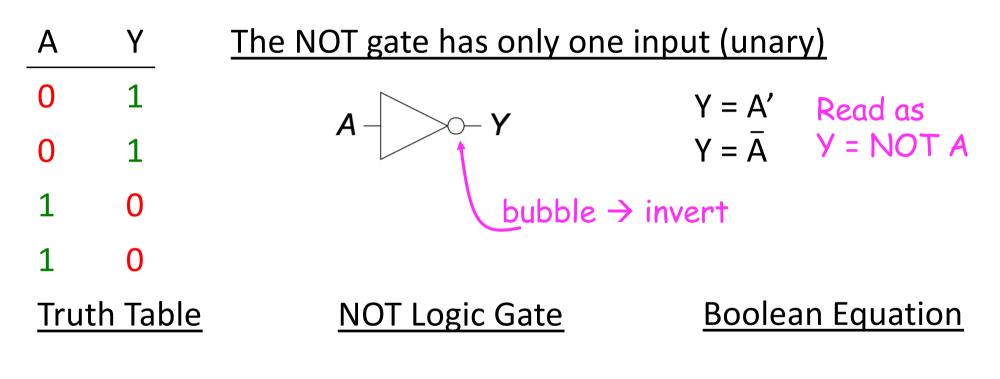

# The NOT Unary Function

NOT Function: The output Y is the inverse of the input A The NOT gate is also known as an inverter

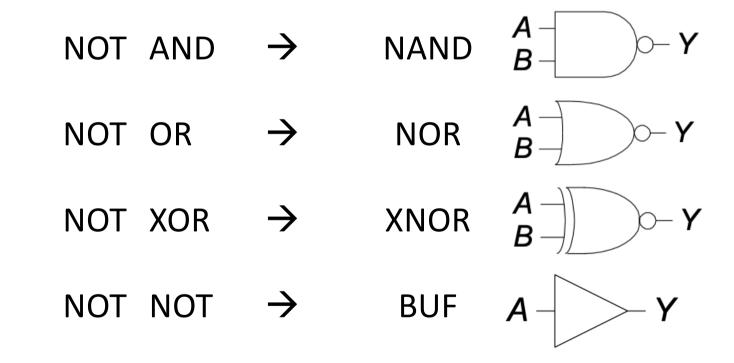

### **Inverting a Gate's Operation**

Any gate can be followed by a bubble to invert its operation

# In Boolean logic, two wrongs make a right!

We say that two bubbles cancel each other's effect

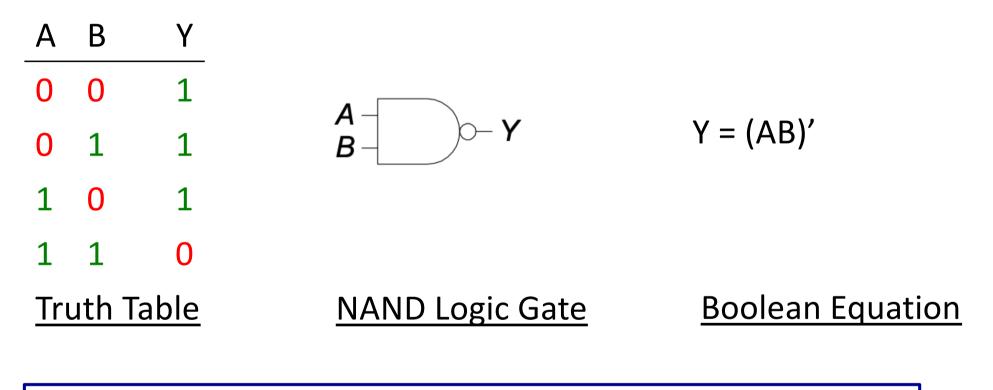

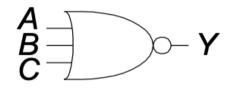

# **The NAND Function**

NAND Function: *The output Y is 1 unless both inputs are 1*

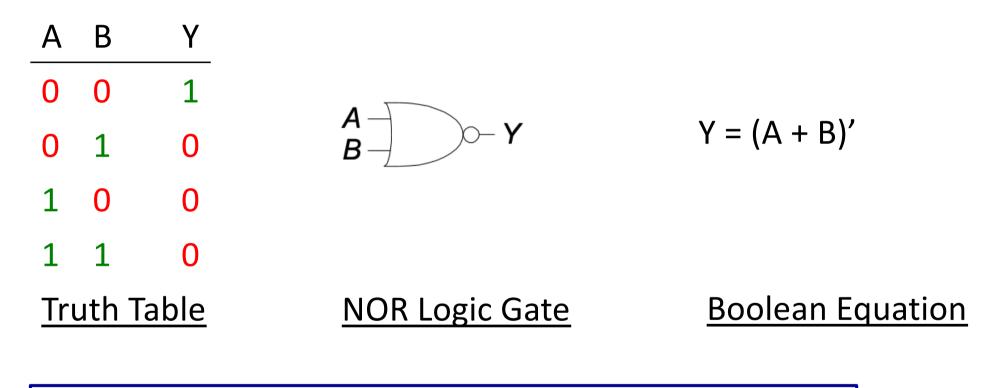

# **The NOR Function**

NOR Function: *The output Y is 1 if neither A nor B is 1*

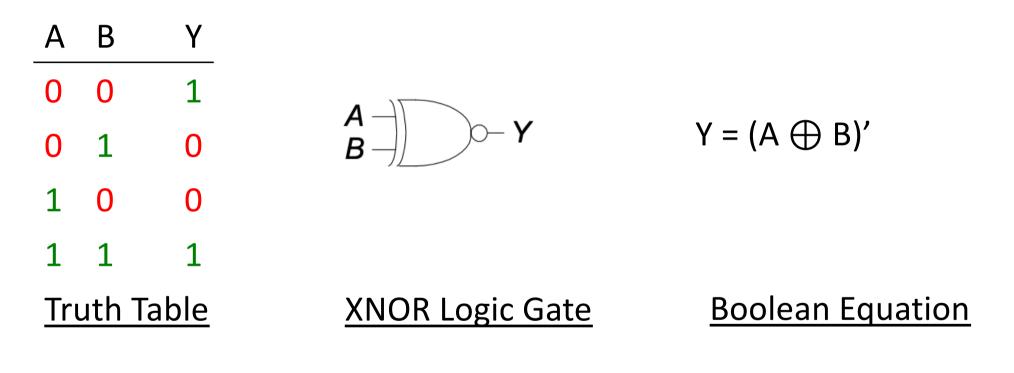

# **The XNOR Function**

XNOR Function: *The output Y is 1 if both A and B are 1 or both are 0*

# **XOR and XNOR are special**

| Α | В          | Υ | Α | В           | Υ |

|---|------------|---|---|-------------|---|

| 0 | 0          | 0 | 0 | 0           | 1 |

| 0 | 1          | 1 | 0 | 1           | 0 |

| 1 | 0          | 1 | 1 | 0           | 0 |

| 1 | 1          | 0 | 1 | 1           | 1 |

|   | <u>XOR</u> |   |   | <u>XNOR</u> |   |

XOR: Output is 1 when inputs are not equal (odd number of 1's)

**Parity Gate**

XNOR: Output is 1 when inputs are equal (even number of 1's)

#### **Equality Gate**

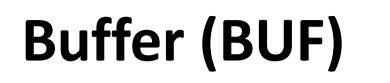

Buffer: The output Y is equal to the input A

# Buffer (BUF)

- At the logic level, BUF is no more useful than a wire

- At a lower level of abstraction (analog level)

- BUF can deliver a large amount of current to a motor

- It can send output to many gates (think of an amplifier)

*Critical to consider multiple layer of abstraction in the compute stack to understand the significance of various elements*

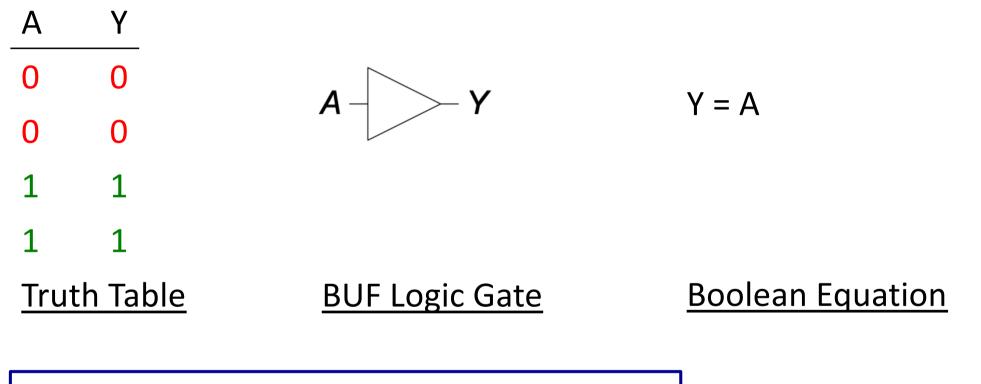

# **Multiple-Input Gates**

| А | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Gates with multiple inputs are possible

Looking at the truth table, can you guess the 3-input gate?

Y = ABC

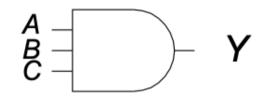

# **Multiple-Input Gates**

| А | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

Gates with multiple inputs are possible

Looking at the truth table, can you guess the 3-input gate?

Y = (A + B + C)'

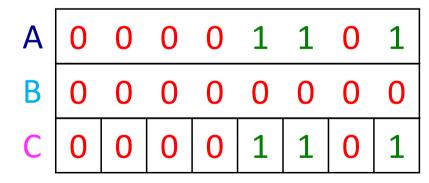

# **Bitwise Operations**

All logical operators can be applied to two bit-patterns (i.e., a group of bits) of *m* bits each, where *m* is any # bits (8, 16, ...)

- Apply the operation individually to each pair of bits

- If A and B are 8-bit input sources (or source operands), then their AND or product, C, is also 8 bits

| C = A + B | (bit-wise | OR) |

|-----------|-----------|-----|

|-----------|-----------|-----|

| Α | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

|---|---|---|---|---|---|---|---|---|

| В | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| С | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

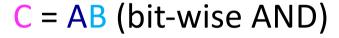

# **Bit Masks**

Suppose we are interested in extracting the least significant four bits from A, while ignoring the right-most four bits

- If we AND A with B, and choose B as 00001111, then we get the desired bit pattern in C

- Bit mask: A binary pattern (B) that separates the bits of A into two halves, the half we care about, and the half we wish to ignore

C = AB (bit-wise AND)

### Exercises

Suppose we have a bit pattern, A = 11000010, and the rightmost two bits are of particular significance. Find a bitmask and a logical operation to mask out the values in the rightmost positions in a new bit pattern C. (All other bits in C are set to 0.)

Suppose we have a bit pattern, A = 10110010, and the leftmost two bits are of particular significance. Find a bitmask and a logical operation to mask out the values in the leftmost positions in a new bit pattern C. (All other bits in C are set to 1.)

### Exercise

Suppose we want to know if two bit-patterns A and B are identical. How can we find out if two bit-patterns are identical?

Verify that, B AND 1 = B, where B is a binary variable. Also, verify that, B OR 0 = B.

Verify that, B AND 0 = 0, where B is a binary variable. Also, verify that, B OR 1 = 1.

### Exercise

Verify that, B AND B = B, where B is a binary variable. Also, verify that, B OR B = B.

Verify that, B AND B' = 0, where B is a binary variable. Also, verify that, B OR B' = 1.

# **Key Ideas**

Any physical quantity can represent TRUE (1) and FALSE (0). Computers use voltage levels for representing one and zero as electronic components such as transistors can distinguish between these two voltage levels. Our ability to shrink transistors has enabled faster computers in a small chip area (400 mm<sup>2</sup> approx.).

Voltage is a continuous physical signal. We can split voltage into as many levels as we want. We use only two levels to represent and manipulate binary variables to simplify circuits.

Using binary variables and Boolean logic to build computers leads to more efficient circuits and computers.

We can do arithmetic in any other base (e.g., 2) without learning Boolean and digital logic. There is nothing special about adding binary numbers compared to adding decimal numbers.

# **Key Ideas**

We need Boolean logic to understand the interaction between binary variables, and understanding the interaction requires us to learn about logic functions. Logic functions can eventually lead us to build more complex digital circuits that solve realworld problems, e.g., adding two large numbers.

We (humans and, more specifically, John von Neumann) found a system of representation for binary numbers called two's complement. This representation simplifies building arithmetic circuits as a single circuit for adding two numbers can handle addition and subtraction. The circuit itself does not know about two's complement. We build circuits and computers today, assuming two's complement signed integers.

# **Classification of Digital Circuits**

Combinational Circuit: Output depends on the current values of the inputs only

- Memoryless (a *distinct* and *critical* feature)

- All logic gates are combinational

Sequential Circuit: Output depends on the current and previous values of the inputs

- The sequence of inputs dictate the output

- Sequential circuits have state or memory

- Example: Elevator controller (**State:** TRANSIT, GROUND, TOP)

### **Combinational Behavior**

**Example:** Suppose a combinational circuit, consisting of an AND gate, with two inputs, A and B

| time <del>&gt;</del> | t0 | t1 | t2 | t2 | t4 | t5 | t6 |

|----------------------|----|----|----|----|----|----|----|

| А                    | 0  | 1  | 1  | 0  | 1  | 0  | 1  |

| В                    | 0  | 1  | 0  | 0  | 1  | 0  | 1  |

| Output               | 0  | 1  | 0  | 0  | 1  | 0  | 1  |

At time t6, the *sequence* of changes to A and B between t0 – t5 is irrelevant. The output is strictly determined by the values of A and B at t6

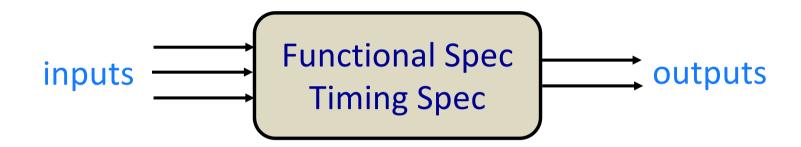

# **Combinational Circuits**

Functional specification: What is the circuit supposed to do? What is the output for a given combination of input values?

Timing specification: How long does the circuit takes to produce the output?

- Worst-case: ten nanoseconds

- Best-case: one nanoseconds

# **Combinational Circuits**

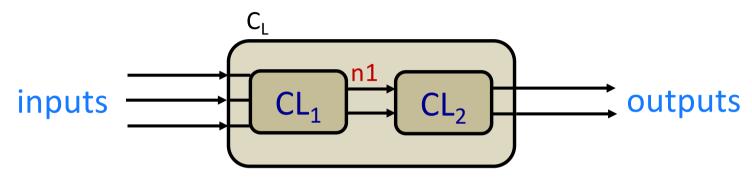

Hierarchy: The top-level circuit,  $C_L$ , is made up for of two subcircuits (also combinational),  $CL_1$  and  $CL_2$

Nodes: n1 is an internal wire or node

Abstraction: The *input and output* interface, and the functional and timing specification is enough for someone to use  $C_L$ . They do not need to know the inner composition of  $C_L$

# Implementing Combinational Logic

Steps in implementing combinational Logic

- 1. Initial specification (e.g., in English)

- 2. Construct the truth table

- 3. Derive the Boolean equation

Functional specification

- 4. Simplify the Boolean equation (use Boolean algebra)

- 5. Implement the equation using logic gates

# Specification

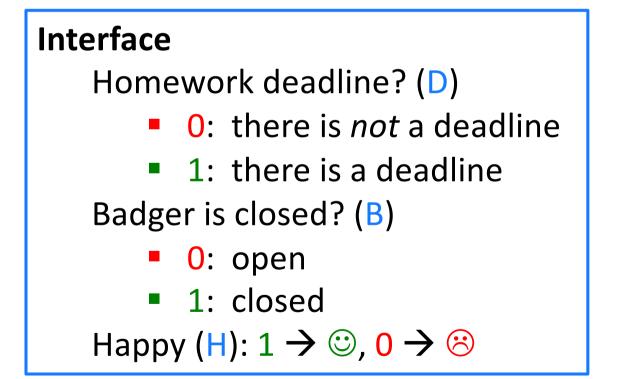

[Happiness detector] The students are back on campus. They are not *happy* if there is a *homework* deadline, or *Badger & Co.* is closed. Design a circuit that will output 1 only if students are happy.

[Multiplexer] Design a circuit with three inputs:  $D_0$ ,  $D_1$ , select; and one output. The output is  $D_0$  if select is 0, and  $D_1$  if select is 1.

**[Half Adder]** Design a circuit that adds two binary variables: A and B. The circuit has two outputs: sum and carry-out (C<sub>out</sub>).

[Full Adder] Design a circuit that adds three binary variables: A, B, and a carry-in (C<sub>in</sub>). The circuit has two outputs: sum and carry-out (C<sub>out</sub>).

# **Constructing Truth Tables**

Identify inputs and outputs (interface)

- The inputs and outputs maybe implicitly specified

- Or, determining them may require some thought

Write all the possible combinations of input values

- For each input combination, determine the output

- All inputs to the left, outputs to the right

# **Truth Table: Happiness Detector**

**Specification:** The students are back on campus. They are **not** *happy* if there is a *homework* deadline, or *Badger* & Co. is closed. Design a circuit that will output 1 only if students are *happy*.

| <u>Truth Table</u> |   |   |  |  |  |

|--------------------|---|---|--|--|--|

| D                  | В | н |  |  |  |

| 0                  | 0 | 1 |  |  |  |

| 0                  | 1 | 0 |  |  |  |

| 1                  | 0 | 0 |  |  |  |

| 1                  | 1 | 0 |  |  |  |

# **Deriving a Boolean Equation**

#### Some Terminology first

- For any binary variable X, its compliment is X'

- True form (X) and complementary form (X') are called *literals*

- AND of one or more literals is called a *product* or *implicant*

- X, Y, XY, X'Y'Z, XYZ, XY'Z' are all implicants for a function of three variables

- Minterm: A product involving all the inputs to the function

- XYZ is a minterm for a function of three variables X, Y, and Z

- XY is not a minterm because it is missing one literal (Z)

# **Deriving a Boolean Equation**

#### Order of operations

- NOT has the highest precedence

- Next is AND

- OR is last

- Example: Y = A + BC'

- First, we find C'

- Then, we find BC' (product/AND)

- Finally, we perform A + (the *result* of BC')

# **Sum-of-Products Form**

To write the Boolean equation for a truth table, *sum each of the minterms for which the output is 1*

| Α | В | Y1 | minterm | name           |

|---|---|----|---------|----------------|

| 0 | 0 | 0  | A'B'    | m <sub>0</sub> |

| 0 | 1 | 1  | A'B     | m <sub>1</sub> |

| 1 | 0 | 0  | AB'     | m <sub>2</sub> |

| 1 | 1 | 0  | AB      | m <sub>3</sub> |

Boolean Eq

Y1 = A'B

Y1 is 1 only when A = 0 and B = 1

Conversely, when A' = 1 and B = 1

# **Sum-of-Products Form**

To write the Boolean equation for a truth table, sum each of the minterms for which the output is 1

| Α | В | Y1 | minterm | name           |

|---|---|----|---------|----------------|

| 0 | 0 | 0  | A'B'    | m <sub>0</sub> |

| 0 | 1 | 1  | A'B     | m <sub>1</sub> |

| 1 | 0 | 0  | AB'     | m <sub>2</sub> |

| 1 | 1 | 1  | AB      | m <sub>3</sub> |

Boolean Eq Y1 = A'B + AB Y1 is 1 *either* when A = 0 and B = 1 OR, when A = 1 and B = 1 Y1 =  $\sum (1,3)$

# **Equation: Happiness Detector**

| <u>Truth Table</u> |   |   |   | <u>Boolean Eq</u> |

|--------------------|---|---|---|-------------------|

|                    | D | В | Н | H = D'B'          |

|                    | 0 | 0 | 1 | H = (D)' AND (B)' |

|                    | 0 | 1 | 0 |                   |

|                    | 1 | 0 | 0 |                   |

|                    | 1 | 1 | 0 |                   |

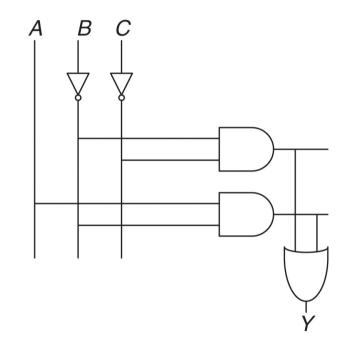

# **From Equation to Gates**

Schematic: A diagram of a digital circuits with elements (gates) and the wires that connect them together

Example Boolean Eq

Y = AB' + B'C'

#### <u>Schematic</u>

- 1. Inputs are on the left (or top) side

- 2. Outputs are on the right

- 3. Gates flow from left to right

- 4. Use straight wires

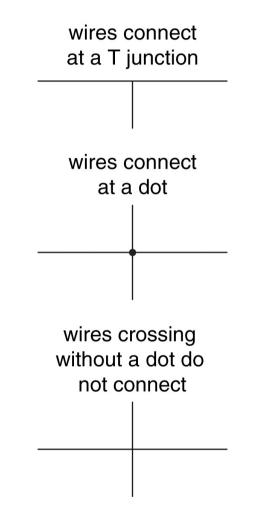

- 5. Wires connect at a T junction

- 6. A dot where wires cross indicates a connection

# **Rules for Connecting Wires**

# **Schematic: Happiness Detector**

| <u>Truth Table</u> |   | <u>Boolean Eq</u> | Logic Gate Implementation |

|--------------------|---|-------------------|---------------------------|

| DB                 | Н | H = D'B'          |                           |

| 0 0                | 1 | H = (D)' AND (B)' | B - H                     |

| 0 1                | 0 |                   |                           |

| 1 0                | 0 |                   |                           |

| 1 1                | 0 |                   |                           |

# **Schematic: Happiness Detector**

| <u>Truth Table</u> |   | <u>Boolean Eq</u>       | Logic Gate Implementation |

|--------------------|---|-------------------------|---------------------------|

| D B                | Η | H = D'B'                |                           |

| 0 0                | 1 | H = (D)' AND (B)'       | B H                       |

| 0 1                | 0 |                         |                           |

| 1 0                | 0 | Which (monolithic) gate |                           |

| 1 1                | 0 | is this?                |                           |

# **Schematic: Happiness Detector**

| <u>Truth Table</u> |   | able | <u>Boolean Eq</u>         | Logic Gate Implementation |

|--------------------|---|------|---------------------------|---------------------------|

| D                  | В | Н    | H = D'B'                  |                           |

| 0                  | 0 | 1    | H = (D)' AND (B)'         | R - H                     |

| 0                  | 1 | 0    |                           |                           |

| 1                  | 0 | 0    | Which (monolithic) gate   |                           |

| 1                  | 1 | 0    | is this? Answer: NOR gate | B - H                     |

# Multiplexer: T. Table + Eq

Specification: Design a circuit with three inputs:  $D_0$ ,  $D_1$ , select (S); and one output (Y). The output is  $D_0$  if select is 0, and  $D_1$  if select is 1.

$$Y = S'D_{1}'D_{0} + S'D_{1}D_{0} + SD_{1}D_{0}' + SD_{1}D_{0}$$

$$Y = S'D_{0} (D_{1}' + D_{1}) + SD_{1} (D_{0}' + D_{0})$$

$$= 1 \qquad = 1$$

$$Y = S'D_{0} (1) + SD_{1} (1)$$

$$Y = S'D_{0} + SD_{1}$$

| <u>Truth Table</u> |       |       |   |  |  |  |  |

|--------------------|-------|-------|---|--|--|--|--|

| S                  | $D_1$ | $D_0$ | Υ |  |  |  |  |

| 0                  | 0     | 0     | 0 |  |  |  |  |

| 0                  | 0     | 1     | 1 |  |  |  |  |

| 0                  | 1     | 0     | 0 |  |  |  |  |

| 0                  | 1     | 1     | 1 |  |  |  |  |

| 1                  | 0     | 0     | 0 |  |  |  |  |

| 1                  | 0     | 1     | 0 |  |  |  |  |

| 1                  | 1     | 0     | 1 |  |  |  |  |

| 1                  | 1     | 1     | 1 |  |  |  |  |

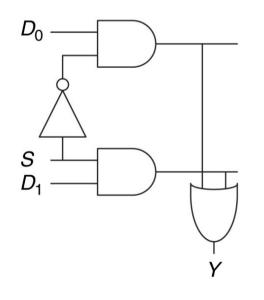

#### **Multiplexer:** Gate-Level Schematic

Specification: Design a circuit with three inputs:  $D_0$ ,  $D_1$ , select (S); and one output (Y). The output is  $D_0$  if select is 0, and  $D_1$  if select is 1.

$\mathbf{Y} = \mathbf{S'}\mathbf{D}_0 + \mathbf{S}\mathbf{D}_1$

**Gate-Level Schematic**

| S | $D_1$ | $D_0$ | Y |

|---|-------|-------|---|

| 0 | 0     | 0     | 0 |

| 0 | 0     | 1     | 1 |

| 0 | 1     | 0     | 0 |

| 0 | 1     | 1     | 1 |

| 1 | 0     | 0     | 0 |

| 1 | 0     | 1     | 0 |

| 1 | 1     | 0     | 1 |

| 1 | 1     | 1     | 1 |

#### Half Adder

**Specification:** Design a circuit that adds two binary variables: A and B. The circuit has two outputs: sum and carry-out (C<sub>out</sub>).

| <u>Truth Table</u> |   |                  |   | <u>Boolean Eq</u>     | <u>Schematic</u> |

|--------------------|---|------------------|---|-----------------------|------------------|

| Α                  | В | C <sub>out</sub> | S | S = A'B + AB'         |                  |

| 0                  | 0 | 0                | 0 | $S = A \bigoplus B$   |                  |

| 0                  | 1 | 0                | 1 | C <sub>out</sub> = AB | Cout             |

| 1                  | 0 | 0                | 1 |                       |                  |

| 1                  | 1 | 1                | 0 |                       |                  |

# Full Adder: T. Table + Eq

Specification: Design a circuit that adds two binary variables: A and B. The circuit has two outputs: sum and carry-out (C<sub>out</sub>).

$S = C_{in}'A'B + C_{in}'AB' + C_{in}A'B' + C_{in}AB$  $C_{out} = C_{in}'AB + C_{in}A'B + C_{in}AB' + C_{in}AB$

Simplification via Boolean algebra  $S = A \bigoplus B \bigoplus C_{in}$  $C_{out} = C_{in}(A \bigoplus B) + AB$

| C <sub>in</sub> | Α | В | C <sub>out</sub> | S |

|-----------------|---|---|------------------|---|

| 0               | 0 | 0 | 0                | 0 |

| 0               | 0 | 1 | 0                | 1 |

| 0               | 1 | 0 | 0                | 1 |

| 0               | 1 | 1 | 1                | 0 |

| 1               | 0 | 0 | 0                | 1 |

| 1               | 0 | 1 | 1                | 0 |

| 1               | 1 | 0 | 1                | 0 |

| 1               | 1 | 1 | 1                | 1 |

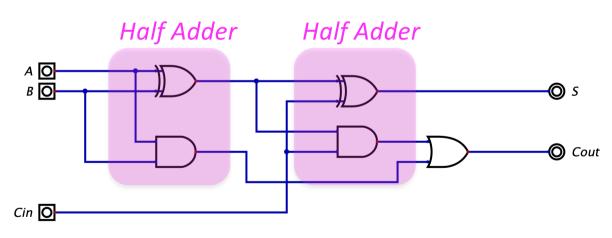

# **Full Adder: Schematic**

Specification: Design a circuit that adds two binary variables: A and B. The circuit has two outputs: sum and carry-out (C<sub>out</sub>).

- ${\color{black}{\mathsf{S}}}={\color{black}{\mathsf{A}}} \oplus {\color{black}{\mathsf{B}}} \oplus {\color{black}{\mathsf{C}}}_{{\color{black}{\mathsf{in}}}}$

- $C_{out} = C_{in}(A \bigoplus B) + AB$

| C <sub>in</sub> | Α | В | C <sub>out</sub> | S |

|-----------------|---|---|------------------|---|

| 0               | 0 | 0 | 0                | 0 |

| 0               | 0 | 1 | 0                | 1 |

| 0               | 1 | 0 | 0                | 1 |

| 0               | 1 | 1 | 1                | 0 |

| 1               | 0 | 0 | 0                | 1 |

| 1               | 0 | 1 | 1                | 0 |

| 1               | 1 | 0 | 1                | 0 |

| 1               | 1 | 1 | 1                | 1 |

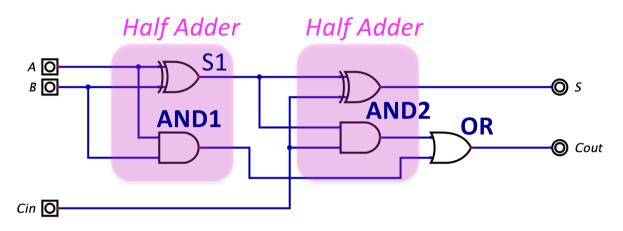

## Full Adder = Two Half Adders

What is **AND1** doing?

Computes the carry out from A + B (call it S1) What is AND2 doing?

Computes the carry out from S1 + C<sub>in</sub>

What is the **OR** gate doing?

- C<sub>out</sub> is 1 if either the output of AND1 is 1 or the output of AND2 is 1

- What does the truth table reveal about C<sub>out</sub>?

| <b>C</b> <sub>in</sub> | Α | В | C <sub>out</sub> | S |

|------------------------|---|---|------------------|---|

| 0                      | 0 | 0 | 0                | 0 |

| 0                      | 0 | 1 | 0                | 1 |

| 0                      | 1 | 0 | 0                | 1 |

| 0                      | 1 | 1 | 1                | 0 |

| 1                      | 0 | 0 | 0                | 1 |

| 1                      | 0 | 1 | 1                | 0 |

| 1                      | 1 | 0 | 1                | 0 |

| 1                      | 1 | 1 | 1                | 1 |